2024/05/18 08:15 1/13 SLICE-FPGA-II Manual

### **RPM-100 Manual**

Model No. RPM-100

Document Last Updated on 2022/09/26 22:51

Please read Limited Warranty and General Warnings and Cautions prior to operating the RPM-100.

#### Links

Click here for the Main Manuals Page.

Click here for the FFC-100 Quick Start Guide.

Click here for the FFC-100 Fiber Frequency Comb Manual Click here for the FFC-100 API.

Click here for the latest version of WinPython

# **Description**

The RPM-100 is an FPGA based locking instrument for use with the FFC-100. Using the included software, the Carrier Envelope Offset and Optical frequencies of the FFC-100 can be locked with ease!

# **List of Warning Symbols**

Warning. Pay special attention to procedures and notes. If procedure is not followed carefully, damage to the FFC-100 or devices connected to it may occur.

Potential for electrical shock hazard.

# **Absolute Maximum Ratings and Power Input**

Note: All modules designed to be operated in a laboratory environment.

| Parameter                     | Rating          |

|-------------------------------|-----------------|

| Environmental Temperature     | >15°C and <30°C |

| Environmental Humidity        | <60%            |

| Environmental Dew Points      | <15°C           |

| Maximum AC Line Input Current | 2 A             |

Tab. 1: Absolute Maximum Ratings

## **Notice**

Do not block the airflow vents on the side of the chassis or the fan inputs & outputs on either the FFC-100 or the SLICE-FPGA.

If this instrument is used in a manner not specified by the manufacturer in this manual or other relevant literature, protection provided by the instrument may be impaired.

Successful implementation of the RPM-100 depends critically on the design of the whole system: FFC-100, phase locking electronics, and any references to which the FFC-100 is locked or vice versa.

# **Specifications**

| Inputs               |                    |  |

|----------------------|--------------------|--|

| Parameter            | Value              |  |

| f <sub>opt</sub>     | -30 ~ 10dBm        |  |

| f <sub>ceo</sub>     | -30 ~ 10dBm        |  |

| External Clock Input | 0dBm <sup>1)</sup> |  |

2024/05/18 08:15 3/13 SLICE-FPGA-II Manual

| Outputs           |                       |  |

|-------------------|-----------------------|--|

| Parameter         | Value                 |  |

| Current Out       | ±10V                  |  |

| PZT Out           | 0V-5V                 |  |

| Analog Slow Servo | ±10V                  |  |

| 10MHz Out         | +3V TTL <sup>2)</sup> |  |

Tab. 2: Specifications of RPM-100 Inputs and Outputs

#### **FPGA Control**

The RPM-100 FPGA Controller can be used to phase lock  $f_{CEO}$  to a reference and  $f_{OPT}$  to a reference laser such as the Rio Planex. If you have not already done so, install WinPython for controlling the RPM-100.

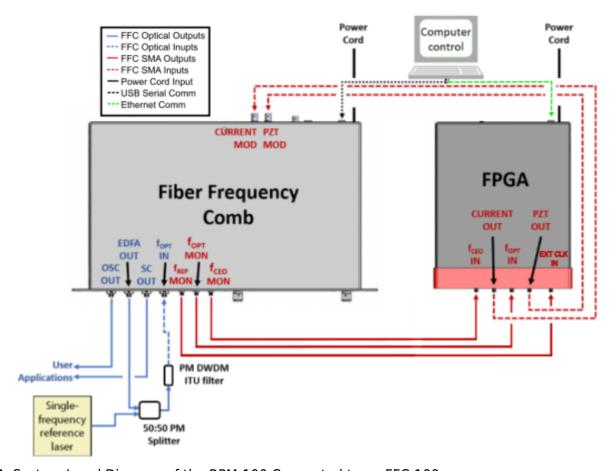

Fig. 4: System Level Diagram of the RPM-100 Connected to an FFC-100

The RPM-100 can be used to phase lock  $f_{\text{CEO}}$  and  $f_{\text{opt}}$ . Locking  $f_{\text{opt}}$  requires a reference CW laser and heterodyne setup (such as a 50:50 beam splitter and DWDM filter). The stability of the lock will depend on the reference laser used. All performance data is collected with a Rio Planex laser.

#### **Specifications**

## **Software Setup**

- Open the "WinPython-64bit-3.6.1.0Qt5" folder after installing WinPython, and launch the Spyder application within this folder.

- Open the "digital\_servo\_python\_gui\_RPM100" folder and locate the GUI control file named "XEM GUI3.py".

- Drag and drop the file into Spyder, and run the script to launch the GUI.

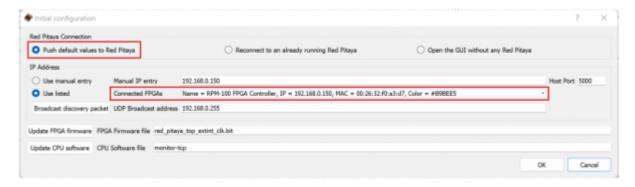

- A start-up menu should appear (figure ??). Check that the software can recognize the ethernet

connection to the module. If the module is recognized, the device name and IP address will

appear next to "Connected FPGAs". If the device is not initially found, click "Broadcast discovery

packet" to search for the device. Ensure "Push default values to Red Pitaya" is selected and

press OK.

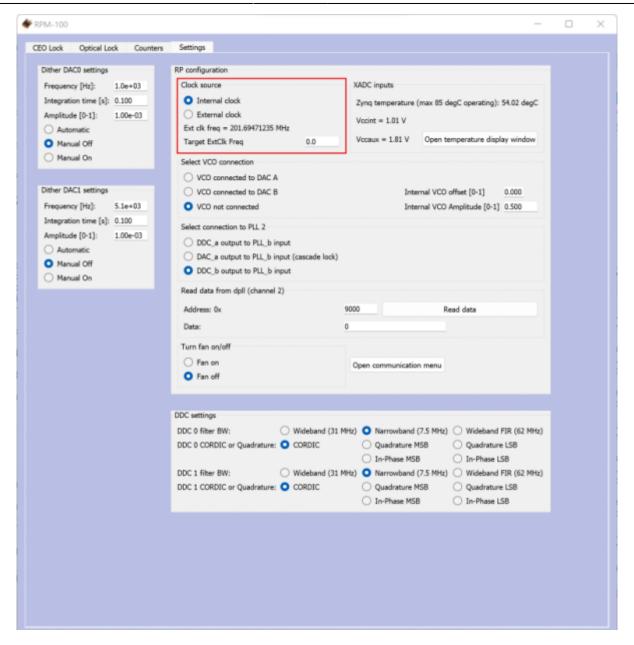

• Navigate to the "Settings" tab and select the appropriate clock signal to be used. If using an external clock, type the frequency (in Hz) of your reference signal.

2024/05/18 08:15 5/13 SLICE-FPGA-II Manual

## **Locking f(CEO)**

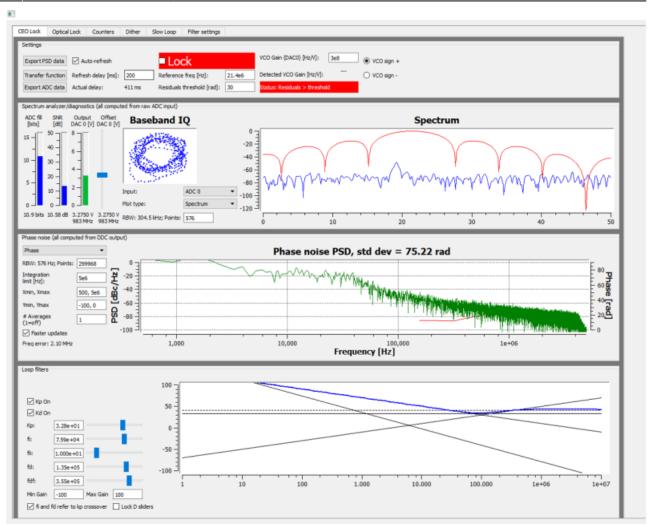

1. Navigate to the "CEO Lock" tab and adjust the "Offset DAC 0" slider near the top left by clicking and dragging the slider until the the data in the Baseband IQ plot is circular (figure 5). This centers the beat note near the reference frequency. It is also possible to adjust the FFC-100 oscillator current on its front panel to make this adjustment.

22:51

Fig. 5: Centering f(CEO) on reference frequency (Baseband IQ optimization)

2. Press the "Lock" button (figure 6, top middle). If the system doesn't lock, change the VCO sign to the opposite polarity (top right) and try again. If the system still won't lock, try lowering the K<sub>D</sub> value (bottom left).

2024/05/18 08:15 7/13 SLICE-FPGA-II Manual

Fig. 6: Locking f(CEO)

## **Locking f(opt)**

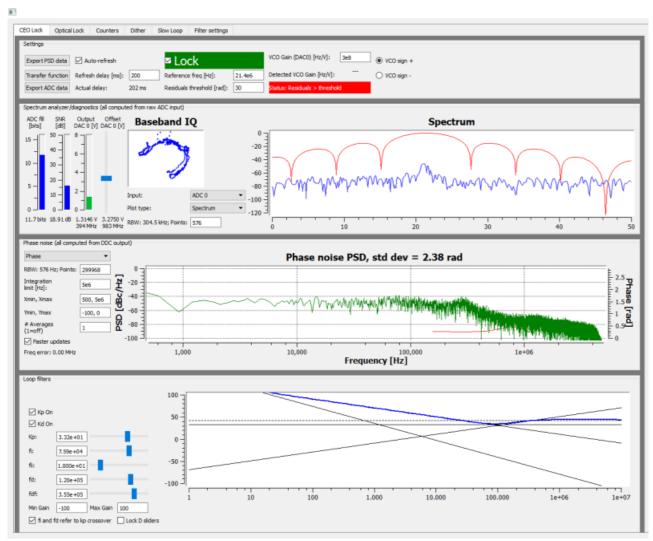

1. Navigate to the "Optical Lock" window. Center the beat note near the reference frequency: adjust the "Offset DAC 1" slider (or your reference laser frequency) until you see a circular Baseband IQ diagram (figure 7).

22:51

Fig. 7: Centerig f(opt) on reference frequency (Baseband IQ optimization)

2. Press the "Lock" button (figure 8). If  $f_{opt}$  doesn't lock, change the VCO sign to the opposite polarity and try again. If the system continues to not lock, lower the K<sub>D</sub> value.\\

2024/05/18 08:15 9/13 SLICE-FPGA-II Manual

Fig. 8: Locking f(opt)

3. Adjust PID settings (bottom middle of figure 8) accordingly to lower the integrated phase noise of each parameter ( $f_{CEO}$  and  $f_{opt}$ ). The default settings provided in the software are a good place to start but tweaking the values can often improve performance.

# **Troubleshooting**

#### **Overview**

In many cases, all that is necessary to get up-and-running with the RPM-100 is to install the correct WinPython distribution, and run the provided GUI software using the WinPython Spyder environment. If you are unable to connect the GUI to the RPM-100, follow the below instructions to eliminate possible causes of failure.

## **Ethernet Controller IP Configuration**

Whatever ethernet port you use to control the RPM-100, it is necessary that your computer identifies itself on this Ethernet port with a fixed IP address in the **192.168.0.x subnet**. Sometimes a computer's default settings do not fit this requirement. From the Windows Control Panel, click through: Network and Internet -> Network and Sharing Center -> Change adapter settings

You will see a number of network adapters listed. You should see one of the network adapters change state when you connect the powered-on RPM-100 to your PC via the ethernet cable, as shown below:

## Before

## After

Watch for this change to identify the correct network adapter.

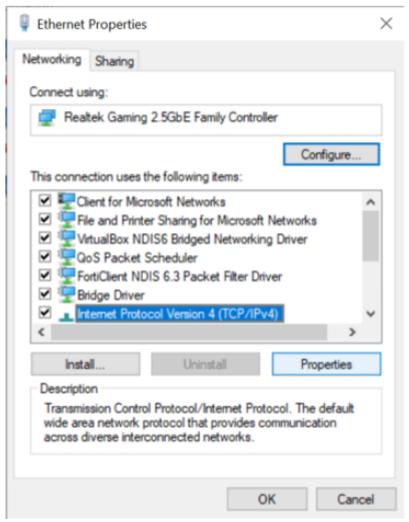

- Right-click on the adapter, and click **Properties**.

- From the screen that appears, click on "Internet Protocol Version 4 (TCP/IPv4)" and then click Properties.

2024/05/18 08:15 11/13 SLICE-FPGA-II Manual

Fig. 10: The Adapter Properties screen, with the IPv4 Settings highlighted

• In the IPv4 Properties Page, select the bubble next to "Use the following IP address:", and fill in the IP Address to be **192.168.0.xxx**, where **xxx** is an integer from 0 to 255, and not **150**, as that is the address used by the RPM-100. In this example, we used 196.

22:51

Fig. 11: The IPv4 Properties page, with the IP Address and Subnet Mask filled in.

The Subnet Mask will default to 255.255.255.0, which is fine.

**NOTE:** If you use this same Ethernet port to connect to another network, these configuration changes could result in connectivity problems with that network. If this poses a problem for you, consider buying a USB-to-Ethernet adapter, and configuring just that adapter for use with the RPM-100.

#### Windows Firewall Rules

If you continue to have trouble connecting to the RPM-100, it's possible that your firewall settings are blocking communications with the device. From the Windows Control Panel, click on System and Security -> Windows Defender Firewall -> Advanced Settings to open up the **Windows Defender** Firewall with Advanced Security manager application. In the left panel of the program, click "Inbound Rules." Then, in the right-hand panel of the program, click "New Rule..." Use the "New Inbound Rule Wizard" to create a new rule to the following specifications:

- Rule Type: Program

- Program: [WINPYTHON INSTALL DIRECTORY]\WinPython-64bit-3.6.1.0Qt5\python-3.6.1.amd64\python.exe

- Action: Allow the connection

- Profile: Domain, Private, and Public

- Name: **Red Pitaya WinPython** (or another name of your choice)

In the left-hand panel, click "Outbound Rules", and then click "New Rule...". Repeat the above Rule

2024/05/18 08:15 13/13 SLICE-FPGA-II Manual

creation steps to create a rule that allows outgoing packets from the WinPython directory's "python.exe" file. Finally, ensure that the aforementioned python.exe file is not being restricted by any other firewall rules.

1)

Do not exceed +10dBm for the protection of the device

2)

at 10MHz

From:

https://www.vescent.com/manuals/ - Product Manuals

Permanent link:

https://www.vescent.com/manuals/doku.php?id=ffc:locking\_electronics:rpm-100&rev=1664232663

Last update: 2022/09/26 22:51